100GBASE-LR4 QSFP28 1310 nm 10 km Hi-Optel HQSFP28-2L2-Modul

Beschreibungen

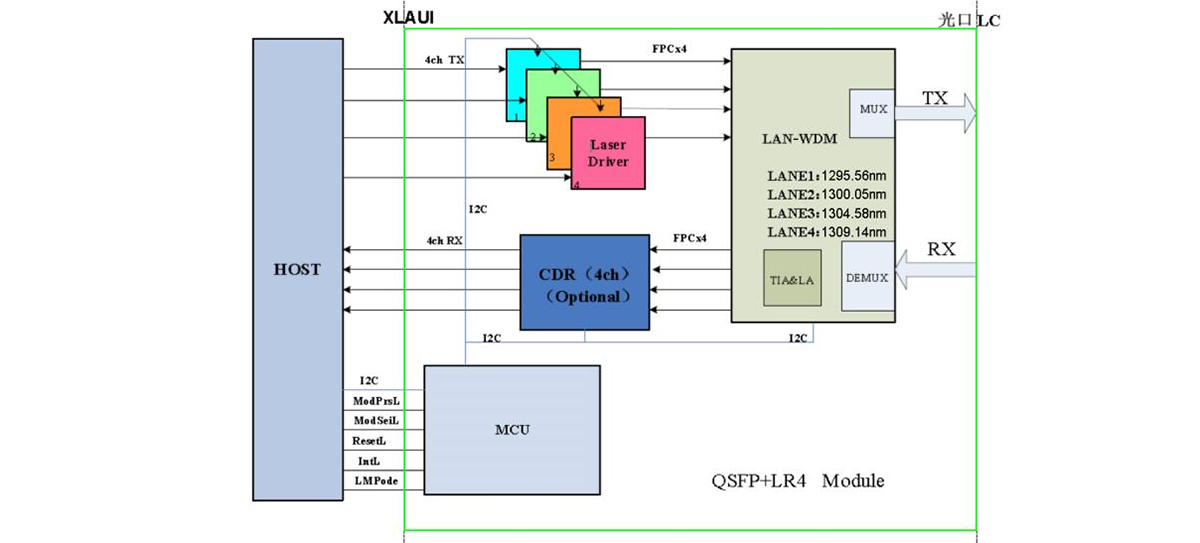

Unten ist ein Blockdiagramm des optischen Transceivers QSFP28 LR4 dargestellt

Merkmale

● Unterstützt eine Gesamtbitrate von 103,1 Gbit/s

● 4 x 25,78 Gbit/s neu getaktete elektrische Schnittstelle

● 4x25,78 Gbit/s DFB-basierter LAN-WDM-Sender und PIN/TIA-Empfänger

● Maximale Verbindungslänge von 10 kmSinglemode-Faser (SMF)

● Hot-plug-fähiger QSFP28-Footprint

● Duplex-LC-Buchsen

● Einzelne 3,3-V-Stromversorgung

● Maximale Verlustleistung <3,5 W

● RoHS-6-konform und bleifrei

● I2C-Verwaltungsschnittstelle

● Gehäusebetriebstemperatur:Gewerblich: 0°C bis +70°C

Anwendung

● 100GBASE-LR4 100G Ethernet

Einhaltung

● QSFP28 MSA.

●IEEE802.3bm und IEEE802.3ba

●SFF-8679

●RoHS

Schnittstelle zur digitalen Diagnoseüberwachung

Beim QSFP28 LR4 ist eine digitale Diagnoseüberwachungsfunktion verfügbar. Echtzeitüberwachung inklusive ModulTemperatur, Modulversorgungsspannung und Überwachung für jeden Sender- und Empfängerkanal.

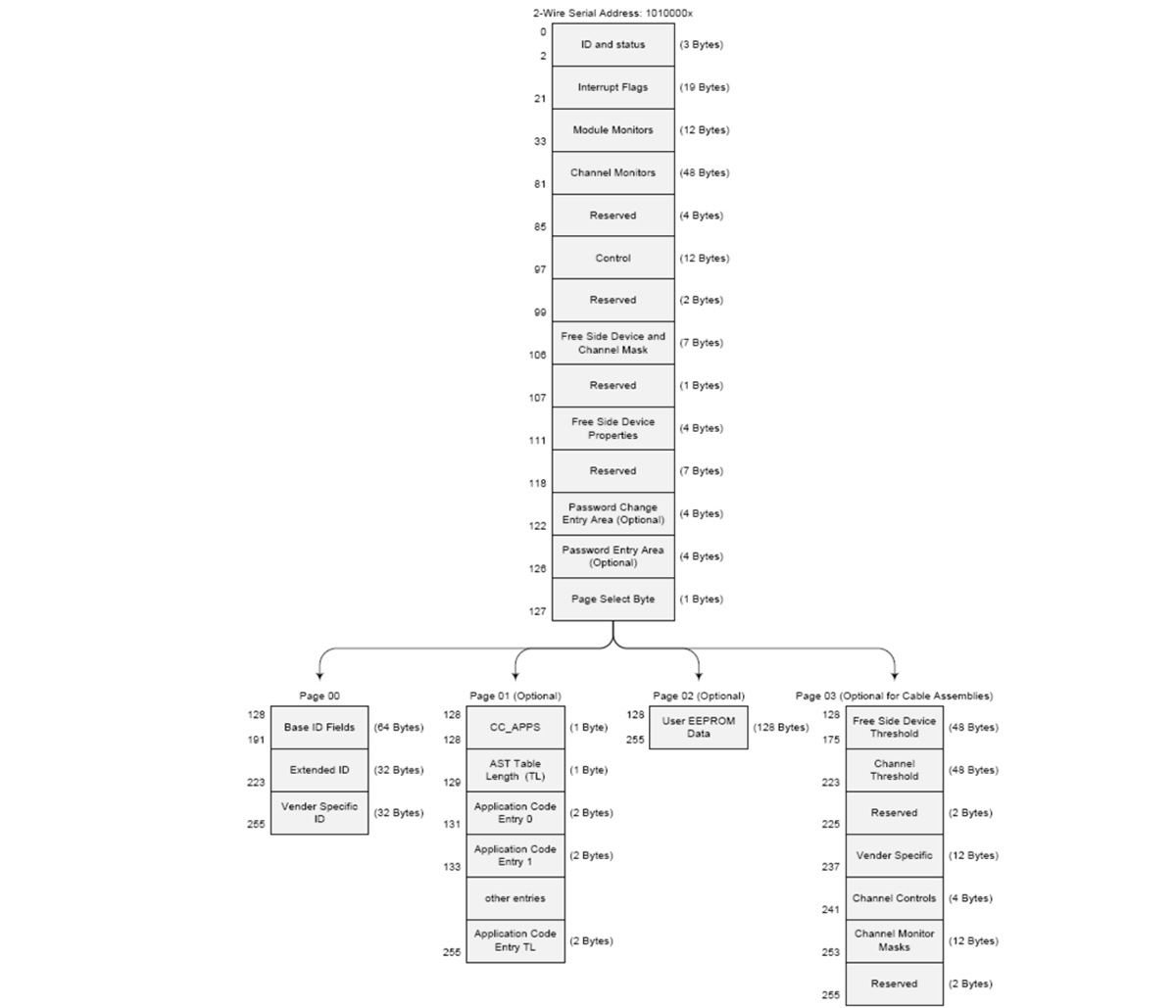

Die Speicherzuordnung für das QSFP28-Modul wird für die serielle ID, die digitale Überwachung und bestimmte Steuerfunktionen verwendet.

Die Schnittstelle ist für alle QSFP28-Geräte obligatorisch. Die Schnittstelle wurde weitgehend nach dem Vorbild des XFP MSA entwickeltwie in INF-8077i Rev.4.0 definiert. Die Speicherkarte wurde geändert, um Platz für 4 optische Geräte zu bietenKanäle und begrenzen den benötigten Speicherplatz. Der Single-Address-Ansatz wird wie in XFP verwendet. Paging istWird verwendet, um zeitkritische Interaktionen zwischen Host und Modul zu ermöglichen.

Die Struktur des Speichers ist in Abbildung 30 dargestellt. Der Speicherplatz ist auf einer unteren, einzelnen Seite angeordnet.Adressraum von 128 Bytes und mehreren oberen Adressraumseiten. Diese Struktur ermöglicht einen zeitnahen Zugriff aufAdressen auf der unteren Seite, z. B. Interrupt-Flags und Monitore. Weniger zeitkritische Eingaben, z. B. SeriennummerInformationen und Schwellenwerteinstellungen sind mit der Seitenauswahlfunktion verfügbar. Die Struktur bietet auchAdresserweiterung durch Hinzufügen zusätzlicher oberer Seiten nach Bedarf. Zum Beispiel in Tabelle 1, obere Seiten 01 und 02sind optional. Die obere Seite 01 ermöglicht die Implementierung der Anwendungsauswahltabelle und die obere Seite 02 ermöglicht die ImplementierungLese-/Schreibbereich des Benutzers. Die untere Seite und die obere Seite 00 werden immer implementiert. Seite 03 ist erforderlich, wenn Byte 2,Bit 2 auf der unteren Seite ist niedrig. Einzelheiten zur Deklaration der optionalen oberen Seiten 01 und 02 finden Sie in Tabelle 39.

Die verwendete Schnittstellenadresse ist A0xh und wird hauptsächlich für zeitkritische Daten wie die Interrupt-Verarbeitung verwendet, um ein „einmaliges Lesen“ aller Daten im Zusammenhang mit einer Interrupt-Situation zu ermöglichen. Nachdem ein Interrupt, IntL, aktiviert wurde, kann der Host das Flag-Feld auslesen, um den betroffenen Kanal und den Flag-Typ zu bestimmen.

Tabelle 1: Digitale Diagnosespeicherkarte (spezifische Datenfeldbeschreibungen).

| Adresse | Beschreibung | Typ | Passives Kupfer, aktives Kupfer, aktive optische | Optisches Modul |

| 0 | Kennung (1 Byte) | Schreibgeschützt | R | R |

| 1-2 | Status (2 Bytes) | Schreibgeschützt | Siehe Tabelle 18 | |

| 3-21 | Interrupt-Flags (19 Bytes) | Schreibgeschützt | Siehe Tabellen 19–21 | |

| 22-33 | Modulmonitore (12 Bytes) | Schreibgeschützt | Siehe Tabelle 22 | |

| 34-81 | Kanalmonitore (48 Bytes) | Schreibgeschützt | Siehe Tabelle 23 | |

| 82-85 | Reserviert (4 Bytes) | Schreibgeschützt | Reserviert | |

| 86-97 | Steuerung (12 Bytes) | Lesen/Schreiben | Siehe Tabelle 24 | |

| 98-99 | Reserviert (2 Bytes) | Lesen/Schreiben | Reserviert | |

| 100-106 | Modul- und Kanalmasken (7 Bytes) | Lesen/Schreiben | Siehe Tabelle 25 | |

| 107-118 | Reserviert (12 Bytes) | Lesen/Schreiben | Reserviert | |

| 119-122 | Eingabebereich für Passwortänderung (optional) (4 Bytes) | Lesen/Schreiben | 0 | 0 |

| 123-126 | Passworteingabebereich (optional) 4 Bytes | Lesen/Schreiben | 0 | 0 |

| 127 | Seite Byte auswählen | Lesen/Schreiben | R | R |